3H3-OS-05b-6

# ニューロモルフィック強誘電体素子を用いた アナログ演算によるパターン認識

Pattern recognition by analog computing using neuromorphic ferroelectric device

上田路人 Michihito Ueda 西谷雄 Yu Nishitani 金子幸広 Yukihiro Kaneko 辻村歩 Avumu Tsujimura

パナソニック株式会社 先端技術研究所

Advanced technology research laboratories, Panasonic corporation

The conductance of a ferroelectric memristor can be modified continuously depending on the height of the applied voltage pulse. We have fabricated a Hopfield neural network circuit by applying ferroelectric memristors and analog integrators to synapses and neurons, respectively. The weights of the synapses corresponding to the learned patterns are modified in parallel by applying spikes in different timings, which indicate the value of the element of a pattern. After learning two patterns, we have succeeded in recalling similar learned pattern by inputting random gray-scaled pattern.

### 1. はじめに

人のように高度な認識機能を、現在のPCで実現することは難しい。その実現のためには、もちろんアルゴリズムの検討も重要であるが、それだけでなくハードウェアについても一体で研究開発していく必要がある。しかし、従来のデジタル方式やアナログ方式を組み合わせたハードウェアを構築するだけでは、その実現は困難と思われる。そこで我々は、デジタル・アナログ両方式の利点を備えた新しい知能情報処理ハードウェアを実現することにより、高度な認識機能の実現を目指している。

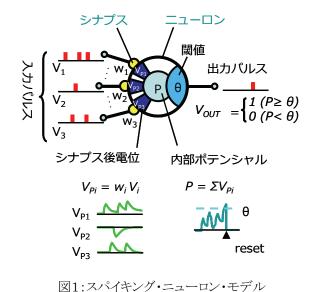

近年、アナログ情報をスパイクの発火タイミングで表現する図1に示すようなスパイキング・ニューロン・モデルが注目されている[1, 2]. スパイキング・ニューロン・モデルは生態模倣の抽象度が高く、ニューロンの振る舞いを細かい時間スケールで表現することができ、より高度な情報処理の実現が期待できる. しかし、

連絡先:上田路人、パナソニック(株)先端技術研究所、 京都府相楽郡精華町光台3-4、 ueda.michihito@jp.panasonic.com

実用的な応用を考えた場合,処理速度や消費電力の観点から,スパイキング・ニューロン・モデルに適したハードウェアが必要となる.スパイキング・ニューロン素子(以下,ニューロ素子と表記)の主要な構成要素は、ニューロン回路とシナプス回路である.中でもシナプス回路は、ニューロン回路に比してその数が多いことから、ニューロ素子の規模や特性に大きな影響を与える.

近年,メモリスタ[3]と呼ばれる多階調にコンダクタンス値を変調できる素子を、ニューロ素子のシナプス回路に適用しようとする研究が盛んである。コンダクタンスとは抵抗の逆数であり、電流の流れやすさを表す指標である。メモリスタは、一般にReRAMなどの2端子素子を指し、高密度実装が可能で、動作も数10ナノ秒程度と高速な上、電源を切ってもそのコンダクタンスを保持できることから、シナプス素子に最適な素子である。しかし、2端子素子であるが故に、コンダクタンスを変調する時と、信号を処理する時で回路の切り替えが必要となってしまう。

筆者らはこれまで強誘電体メモリスタ(FeMEM)と呼ばれるニューロモルフィックな強誘電体素子の検討を行ってきた[4-7]. FeMEM は強誘電体という材料をゲート酸化膜に配したトランジスタであり、印加する電圧パルスの大きさでそのコンダクタンス値をアナログ的に変化し保持できる. FeMEM は3端子素子であるため、コンダクタンス変調と信号処理をシームレスに行えるメリットがある.

## 2. 準備

## 2. 1 強誘電体メモリスタ(FeMEM)の形成

FeMEM はいわゆるボトムゲート型薄膜トランジスタと呼ばれる構造からなり、以下の手順で作製される。制御回路を形成した CMOS 基板に絶縁層を堆積し、電子ビーム蒸着法により厚さ5nmのチタンと厚さ30nmの白金電極を堆積しゲート電極を形成する。次にパルス・レーザ・デポジション(PLD)法により、厚さ250nmのチタン酸ジルコン酸鉛(以下、PZT)からなる強誘電体を形成する。さらにPLD法により酸化亜鉛を60nm形成し半導体層を形成する。最後に、所定の形状のレジストを形成した後に、電子ビーム蒸着法により厚さ30nmの白金電極を堆積し、その後レジストをリフトオフ除去することで、ソース電極とドレイン電極を形成する。

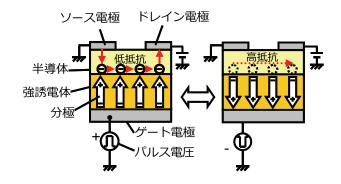

FeMEM はゲート電極にパルス電圧を加えることで、強誘電体内部の分極というイオンの偏りを変化させることで動作させる.

図2:強誘電体メモリスタの構造と動作原理

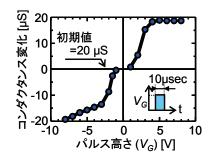

図3:電圧パルスによるコンダクタンス変調

強誘電体は、電圧をゼロに戻しても分極がゼロにならず、残留分極が残るという特徴を持つ.分極は図2では、正に帯電している方が矢印の先になるように表記している.ゲート電極にプラスのパルス電圧を印加すると分極が上向きとなる.この場合、酸化亜鉛中の電子が強誘電体界面に引き寄せられるたため、ソース・ドレイン間(以下、チャネル)は電子が流れやすくなり、高コンダクタンスとなる.逆にゲート電極にマイナスのパルス電圧を印加すると、分極は下向きとなり、酸化亜鉛中の電子は反発され、数が少なくなるため、チャネルは電子が流れにくくなり、低コンダクタンスとなる.

このチャネルコンダクタンスは、電圧パルスの極性や大きさで 多階調に変化させることができる(図3).この性質を利用することで、非常に省電力で動作しアナログ階調を有する不揮発可変 コンダクタンス素子が実現できる.

## 2.2 ニューロン回路

FeMEM のコンダクタンスを変化させることで、ドレイン電極にパルス電圧を印加した際に流れる電荷の量を制御することができる. パルスの極性を変えれば、電荷を逆方向に流すことも可能である. このような特性を応用すれば、興奮性・抑制性シナプス回路を構築できる. これにより複数のシナプスを経由する電荷の出入りを積分することで、アナログ積和演算を実現できる.

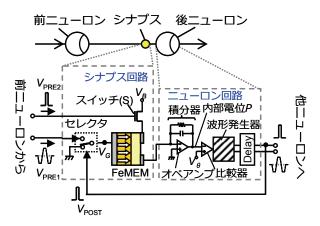

図4には、このような性質を応用したニューロン回路の構成を示している。シナプス回路は、FeMEM と複数のスイッチで構成され、3つのパルスが入力される。 $V_{PREI}$ と  $V_{POST}$ はセレクタと示した部分に入力され、相互の時間差で FeMEM のゲート電圧への電圧パルス  $V_G$ の大きさを変化させる。これにより FeMEM のコンダクタンスが変調される。 $V_{PRE2}$  はスイッチ(S)を制御し、FeMEM を流れる電流を制御する。流れる電流の向きは  $V_B$  で設定する。これにより興奮性・抑制性シナプスが再現され、シナプス荷重が正負いずれの数値の場合も表現できるようになる。

図4:ニューロン回路構成

図5:学習パターン

ニューロン回路はアナログ積分器,比較器と波形発生器で構成している。スイッチが開くと,FeMEMのコンダクタンスに応じた電流が積分器へ流入され,積分器出力Pが上昇する。Pはニューロン細胞の内部ポテンシャルに相当する。スイッチが閉じるとコンデンサに積分された電荷が,コンデンサ両端につなげられた抵抗素子を経て放電されて,Pは減少する。Pが比較器の閾値電圧 $V_{\theta}$ に到達すると,波形発生器により2つの形状のスパイクが発生させられる。2つのスパイクは所定のディレイ時間後,他のニューロンへ向けて出力される。ここではシナプスが1つのみの場合を示したが,実際には複数の前ニューロンからの入力が別々のシナプス回路を経て後ニューロンへ流入する。このような回路をネットワーク化することで,アナログニューラルネットワーク回路を構成した。

## 3. 実験

9個のニューロンからなるホップフィールド・ネットワークにより、ニューロン回路の動作を検証した[2]. シナプスは興奮性と抑制性の2つを準備したため、その総数は144個である.

### 3. 1 学習動作

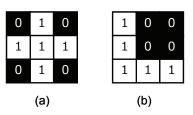

図5に示す「+」と「L」形状の2つの3×3の2値パターンを記憶した. パターン記憶のためには、パターンに対応したシナプス・コンダクタンスのマトリクスへ変化させなければならない. このコンダクタンス変調を、筆者らはスパイク時間差で実現した. 脳のシナプスの荷重は、シナプス前後のニューロンの発火の時間差に依存して変化することが知られている. この現象は、STDP (Spike-Timing-Dependent synaptic Plasticity)と呼ばれており、脳の学習機能と深く関与していると言われている[8].

図6:スパイク時間差による学習

図7:学習過程でのコンダクタンス変化

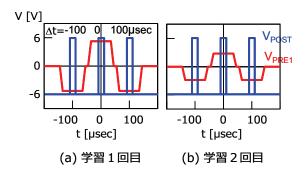

学習には、図6に示すようなスパイク波形  $V_{PREI}$  と  $V_{POST}$  を用いた.  $V_{POST}$  は3つのパルスを記したが、実際には  $V_{PREI}$  との相互の時間差に応じいずれかが印加される.

学習パターンの数値が1ならば 0  $\mu$ sec に、数値が0ならば 100  $\mu$ sec にスパイク中心が来るように、ニューロン回路の波形発生器からスパイクを発生させる。すると、図6(a)の学習1回目のときは、 $\Delta t = -100$ , 0, 100  $\mu$ sec の場合、それぞれ  $V_G = -5$ , 5, 5 V が印加される。図6(b)の学習2回目では、 $V_{PREI}$ を-2.5~2.5 Vの範囲とすることで、 $V_G$ を小さくしていく。

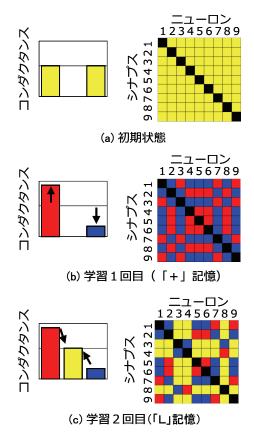

学習過程での FeMEM のコンダクタンス変化を図7に示した. 初期状態では、FeMEM のコンダクタンスが制御範囲の中間値 となるように揃えておく. その後、学習1回目で  $V_G$ = -5、5 Vのいずれかが印加され、コンダクタンスは High / Low の2値となる.

図8:内部電位の挙動

次に学習2回目では  $V_G$ = -2.5、2.5 Vが印加される. High からはそれ以上コンダクタンスが上がらないので、状態維持かやや減少の二通りに分岐する. Low からはコンダクタンスがそれ以上下がらないので、状態維持かやや上昇の二通りに分岐する. 結果として学習2回目ではコンダクタンスは図7(c)に示すように3値となる. 図7には、興奮性シナプスのコンダクタンスのマトリクスを示したが、学習の進行とともに、マトリクスは複雑に変化していく様子が分かる.

学習パターンに対応するタイミングで波形発生器からスパイクを発生させることで、全てのシナプスが即座に並列的に学習可能である.

### 3.2 想起動作

2つのパターンを学習したネットワークに対し、波形発生器からランダムな出力パターン  $V_{POST}$ を出力する。所定のディレイ時間後、これらが次の入力パルス  $V_{PRE2}$ となるため、その応答を観察する。1つのニューロンには他の8つのニューロンからの出力が入力される。各入力に対し、興奮性シナプスと抑制性シナプスのコンダクタンスに対応して荷重の極性と大きさが変化し、これにより積分器への電荷が増減してその出力は複雑な挙動を示す。これがアナログの積和演算に相当する。 $V_{PREI}$  は想起動作時は発生させず、接地電位としておく。この場合、学習は進行しない。

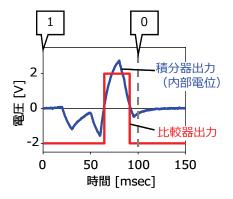

これらの代表的な動作を図8に示した。 $0\sim100$  msec の間にランダムに入力される8つのパルス  $V_{PRE2}$  が入力されると,荷重の極性と大きさに応じ,内部電位が変化している。パルスの幅は 20 msec で一定とした。ほとんど荷重がゼロのシナプスでは入力パルスに対応して内部電位は変化しない。またパルスが重複して入力される場合には,内部電位の変曲点として観察されるなど,波形は,実際には複雑な応答を表している。

比較器の閾値を 0.2 V に設定したところ, 内部電位の変化に対し, 70 msec 程度で比較器が High 信号を出力している. この信号を受けて波形発生器がスパイクを発生し, 所定のディレイ時間(今回は 200 msec に設定)の後, 次の入力パルス群となる. この動作が繰り返され, 想起動作が進行していく.

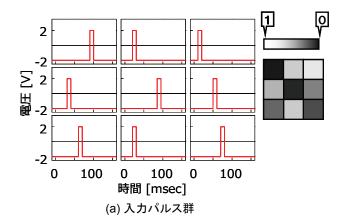

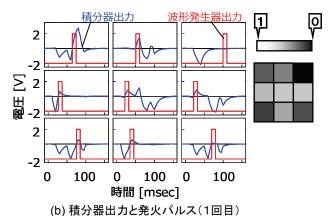

図9に想起動作の結果を示す. 初期値として図9(a)に示すようなパルス群を入力した. これをグレースケールで示した図も併せて示した. これらの信号は接続されたシナプスを経由してその大きさや極性を変えながら,他の8つのニューロンに入力され,積分器の出力を変化させる. いずれのニューロンでも同様

(c) 積分器出力と発火パルス(2回目)

図9:想起動作

に発火が発生し、これが次の入力信号として同様にニューロンの内部電位が変化していく.

図9(b)には各ニューロンの積分器出力と、それにより発生した波形発生器出力パルスを示している。またそのグレースケールを同様に示した。図9(c)には、さらにこの出力パルスを入力とした次の発火状況を示している。右のグレースケール表記を順に見ると、記憶した「+」パターンに近づいてきており、想起動作が実現されていることが分かる。ランダム入力パターンと学習パターンのマンハッタン距離を計算すると、「+」パターンとは3.8、「L」パターンとは5.1 であったことから、距離が近い方のパターンを正しく想起できたことが確認できた。

FeMEM をシナプス素子とするホップフィールドネットワークが, 所望の動作をした. これにより,FeMEM がシナプス素子として, 良好な動作をしていることが確認された.

# 4. おわりに

FeMEM をシナプスとし、スパイク時間差による学習処理をすることで、容易に記憶パターンを FeMEM のコンダクタンス値として学習させることに成功した。また、ホップフィールドネットワーク回路として動作させることで、学習したコンダクタンスが保持され、アナログニューラルネット素子として所望の動作をすることを確認した。特に想起の際の積和演算は、アナログ回路としての過渡応答で実行されることから、省電力が期待される。

しかしながら今回の結果はまだハードウェアとしての原理検証の段階である。ニューラルネットワーク素子としての汎用性を考えるなら、バック・プロパゲーションなど他の方式についても検討が必要である。その際、FeMEM の特性をうまく応用した独自の学習アルゴリズムを検討している。これが実現されれば、駆動が容易になり高速学習が可能となるだけでなく、素子のデジタル制御部を大きく削減できることから、消費エネルギーが大幅に低減できる。ニューロモルフィック素子を用いた演算デバイスは、さらに魅力的なものとなるだろう。

## 参考文献

- [1] W. Gerstner and W. Kistler: Spiking Neuron Models. Single Neurons, Populations, Plasticity (Cambridge University Press, Cambridge, 2002).

- [2] H. Tanaka, T. Morie, and K. Aihara, "A CMOS Spiking Neural Network Circuit with Symmetric/Asymmetric STDP Function," IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences, vol. 92, pp. 1690-1698, 2009.

- [3] D. B. Strukov, G. S. Snider, D. R. Stewart, and R. S. Williams, "The missing memristor found," Nature, vol. 453, pp. 80-83, 2008.

- [4] Y. Kato, Y. Kaneko, H. Tanaka, K. Kaibara, S. Koyama, K. Isogai, T. Yamada, and Y. Shimada, "Overview and Future Challenge of Ferroelectric Random Access Memory Technologies," Japanese Journal of Applied Physics, vol. 46, pp. 2157-2163, 2007.

- [5] Y. Kaneko, Y. Nishitani, H. Tanaka, M. Ueda, Y. Kato, E. Tokumitsu, and E. Fujii, "Correlated motion dynamics of electron channels and domain walls in a ferroelectric-gate thin-film transistor consisting of a ZnO/Pb(Zr,Ti)O<sub>3</sub> stacked structure," J. Appl. Phys., vol. 110, p. 084106, 2011.

- [6] Y. Kaneko, Y. Nishitani, M. Ueda, E. Tokumitsu, and E. Fujii, "A 60 nm channel length ferroelectric-gate field-effect transistor capable of fast switching and multilevel programming," Applied Physics Letters, vol. 99, p. 182902, 2011.

- [7] M. Ueda, Y. Kaneko, Y. Nishitani, T. Morie, and E. Fujii, "Biologically-inspired learning device using three-terminal ferroelectric memristor," in 70th Annual Device Research Conference (DRC), pp. 275-276, 2012.

- [8] G. Bi and M. Poo, "Synaptic modifications in cultured hippocampal neurons: dependence on spike timing, synaptic strength, and postsynaptic cell type," The Journal of Neuroscience, vol. 18, pp. 10464-10472, 1998.